# UNIVERSITY OF SWAZILAND SUPPLEMENTARY EXAMINATION JULY 2016

# FACULTY OF SCIENCE AND ENGINEERING

# DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

TITLE OF PAPER: MICROCONTROLLERS AND MICROCOMPUTER SYSTEMS

COURSE CODE: EE423

TIME ALLOWED: THREE HOURS

# **INSTRUCTIONS:**

.

÷

- 1. There are four questions in this paper. Answer all questions. Each question carries 25 marks.

- 2. If you think not enough data has been given in any question, you may assume any reasonable values stating your assumptions in each case.

# THIS PAPER SHOULD NOT BE OPENED UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR

# THIS PAPER CONTAINS FIVE (5) PAGES INCLUDING THIS PAGE

## **QUESTION ONE (25 marks)**

(a) (i) State the difference between Von-Neumann and Harvard architectures.

(2 marks)

(ii) State some features of a CISC type microprocessor.

(2 marks)

(iii) In an assembly program for a 16F84A, includes instructions 'crunch equ 12Dh' and 'index equ 1Eh'. Using them, write the machine instructions (op codes) for the following assembly statements.

and wf index 0

| unuwj | macs, 0 | USJ  | таел, Э         |

|-------|---------|------|-----------------|

| addlw | .35     | goto | c <b>r</b> unch |

(4 marks)

(b) A section of a program using 16F84A with a 8MHz crystal is shown in Figure-Q1.

| bsf   | status,5    |

|-------|-------------|

| movlw | b'11000101' |

| movwf | option_reg  |

### Figure-Q1

(i) State what is expected from the three statements in Figure-Q1.

(4 marks)

(ii) Calculate the frequency of timer input signal.

(3 marks)

- (c) An application based on a 16F84A using a crystal clock oscillator, requires the timer to overflow in each 8ms.

- (i) Select a suitable one from 1.8432MHz, 2.4576MHz, 3.579MHz and 4MHz crystals, which will give a minimum timing error. Also justify your answer.

(6 marks)

(ii) What is the percentage timing error expected for your selection?

(2 marks)

(iii) How do you configure the option register to meet your selection in (i) above?(2 marks)

## **QUESTION TWO (25 marks)**

Consider the subroutine shown in Figure-Q2. Assume that it is run in a 16F84A clocked with a *8MHz* crystal.

| (i) Calculate the delay that will be provided by this subrouti | ne. |

|----------------------------------------------------------------|-----|

|----------------------------------------------------------------|-----|

- (ii) How do you obtain a delay as close as possible to 0.5ms?

- (iii) Construct a subroutine that will give a delay as close as possible to 10ms using (ii) above with an aid of a flow chart. Your method must aim for a short program length and must show the necessary calculations required.

- (iv) Write the assembly code for (iii) above.

(4 marks)

(11 marks)

(4 marks)

(3 marks)

(v) What is the actual delay produced by your subroutine in (iii) above?

(3 marks)

| delay<br>loop | movlw<br>movwf<br>nop<br>nop<br>decfsz<br>goto<br>return | D2<br>reg<br>reg,1<br>loop |

|---------------|----------------------------------------------------------|----------------------------|

|               | return                                                   |                            |

Figure-Q2

Page 3 of 5

## **QUESTION THREE (25 marks)**

- (a) The PortB(0) to PortB(6) pins of a 16F84A is connected to a common cathode seven segment LED display 'a' to 'g' respectively. The microcontroller runs on a RC clock oscillator of 60KHz.

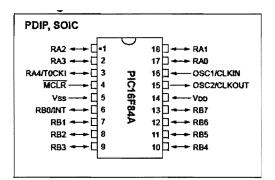

- Draw the complete circuit diagram marking the 16F84A pin numbers clearly.

You may show the clock oscillator R and C without values.

(5 marks)

(ii) Construct a program flow chart/s with sufficient details and labels, which will display '16F' character by character in a continuous loop. Each character must be visible for 0.5sec. The flow charts of any subroutines must be given and the calculation of the values used must also be shown.

(14 marks)

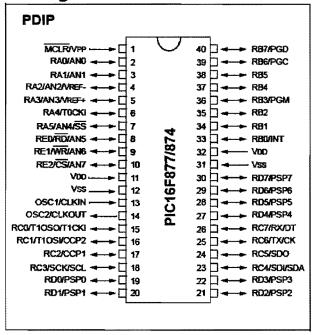

- (b) A serial temperature sensor is connected to the SPI communication port of a 16F877 which acts as the master. The microcontroller is running on a 3.579MHz crystal oscillator.

- Draw a connection diagram between 16F877 and the sensor, giving the usual pin names. Also mark the relevant pin numbers of 16F877 used for this case.

(3 marks)

(ii) If the SSPSTAT and SSPCON registers are configured as 40h and 21h respectively, comment on the data rate limitations of the sensor.

(3 marks)

### **QUESTION FOUR (25 marks)**

- (a) In an assembly program for 16F84A, the *INTCON* register is set to *A8h*.

- (i) Describe the settings of the *INTCON* register.

(2 marks)

Page 5 of 5

(ii) When the program is executed, at a certain point the value of *INTCON* register is *2Dh*. Explain what is described by the *INTCON* register at this instant.

(3 marks)

(iii) State the essential features to be included in an interrupt service routine.

(3 marks)

(iv) The microcontroller is provided with a 4.096MHz crystal oscillator and it is required to produce an interrupt in every  $500\mu s$ . Show a simple method to achieve this and give the settings of relevant registers. What is the value of *INTCON*, just after such an interrupt?

(5 marks)

- (b) An application uses the Analog to Digital Converter (ADC) of a 16F877.

- (i) The ADC is configured to have external voltage reference, four analog inputs, input channel 1 selected for the conversion and ADC turned ON. If the conversion is not yet started, show the settings of the relevant registers. State your assumptions.

(5 marks)

(ii) If the conversion is started and not yet finished, show the contents of these registers.

(2 marks)

(iii) If a 4.096MHz crystal oscillator is used, select values for ADCS1 and ADCS0 bits in the ADCON0 register justifying the answer.

(3 marks)

(iv) What is the minimum acquisition time and the minimum conversion time considering the values in (iii) above?

(2 marks)

SS

# PIC 16F84A

| File Addre | SS                                              | F                                 | ile Addre  |

|------------|-------------------------------------------------|-----------------------------------|------------|

| 00h        | Indirect addr.(1)                               | Indirect addr. <sup>(1)</sup>     | 80h        |

| 01h        | TMR0                                            | OPTION_REG                        | 81h        |

| 02h        | PCL                                             | PCL                               | 82h        |

| 03h        | STATUS                                          | STATUS                            | 83h        |

| 04h        | FSR                                             | FSR                               | 84h        |

| 05h        | PORTA                                           | TRISA                             | 85h        |

| 06h        | PORTB                                           | TRISB                             | 86h        |

| 07h        | 有这个些本于是                                         |                                   | 87h        |

| 08h        | EEDATA                                          | EECON1                            | 88h        |

| 09h        | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h        |

| 0Ah        | PCLATH                                          | PCLATH                            | 8Ah        |

| 0Bh        | INTCON                                          | INTCON                            | 88h        |

| 0Ch        | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 | 8Ch        |

| 4Fh<br>50h |                                                 |                                   | CFh<br>D0h |

### STATUS REGISTER (ADDRESS 03h, 83h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | י Z   | DC    | C     |

| bit 7 |       |       |     |     |       |       | bit 0 |

Unimplemented: Maintain as '0'

RP0: Register Bank Select bits (used for direct addressing)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

TO: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

DC: Digit carry/Dorrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

C: Carry/Dorrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note: A subtraction is executed by adding the two's complement of the second operand. For rotete (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

Data Page 1 of 9

# PIC 16F84A

#### **OPTION REGISTER (ADDRESS 81h)**

|   | R/W-1 | R/W-1  | R/W-1 | R/W-1 | RW-1 | R/W-1 | R/W-1 | R/W-1 |

|---|-------|--------|-------|-------|------|-------|-------|-------|

| ſ | RBPU  | INTEDG | TOCS  | TOSE  | PSA  | PS2   | PS1   | PS0   |

|   | bit 7 |        |       |       |      |       |       | bit 0 |

# RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

TOCS: TMR0 Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

TOSE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/T0CKI pin

PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

#### PS2:PS0: Prescaler Rate Select bits

Bit Value TMR0 Rate WDT Rate

| 000 | 1:2   | 1:1   |

|-----|-------|-------|

| 001 | 1:4   | 1:2   |

| 010 | 1.8   | 1:4   |

| 011 | 1:16  | 1:8   |

| 100 | 1:32  | 1:16  |

| 101 | 1:64  | 1:32  |

| 110 | 1:128 | 1:64  |

| 111 | 1:256 | 1:128 |

|     |       |       |

#### INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | <b>R/W-</b> 0 | R/W-x |  |

|-------|-------|-------|-------|-------|-------|---------------|-------|--|

| GIE   | EEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF          | RBIF  |  |

| bit 7 |       |       |       |       |       |               | bit 0 |  |

GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

EEIE: EE Write Complete Interrupt Enable bit

1 = Enables the EE Write Complete interrupts

0 = Disables the EE Write Complete interrupt

TOIE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

INTE: RB0/INT External Interrupt Enable bit

1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

TOIF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

0 = TMR0 register did not overflow

INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

# 16F84A and 16F877

, **\***

| Mnemo                                                                                                                                                                                                                                                                                                                                                                                       | onic.       |                              |         |       | 14-Bit | Opcode      | •           | Status  |       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------|---------|-------|--------|-------------|-------------|---------|-------|

| ADDWFf, dAdd W and fANDWFf, dAND W with fCLRFfClear fCLRW-Clear WCOMFf, dComplement fDECFf, dDecrement fDECFSZf, dDecrement fINCFf, dIncrement fINCFSZf, dIncrement fINCFSZf, dIncrement fNOVFf, dInclusive OR W with fMOVFf, dMove fMOVWFfMove W to fNOP-No OperationRLFf, dRotate Right f through CarrySUBWFf, dSubtract W from fSWAPFf, dSwap nibbles in fXORWFf, dExclusive OR W with f | Description | Cycles                       | MSD     |       |        | LSb         | Affected    | Notes   |       |

|                                                                                                                                                                                                                                                                                                                                                                                             |             | BYTE-ORIENTED FILE REGIS     | TER OPE | RATIO | NS     |             |             |         |       |

| ADDWF                                                                                                                                                                                                                                                                                                                                                                                       | f, d        | Add W and f                  | 1       | 00    | 0111   | dfff        | ffff        | C,DC,Z  | 1,2   |

| ANDWF                                                                                                                                                                                                                                                                                                                                                                                       | f, d        | AND W with f                 | 1       | 00    | 0101   | dfff        | ffff        | Z       | 1,2   |

| CLRF                                                                                                                                                                                                                                                                                                                                                                                        | 1           | Clear f                      | 1       | 00    | 0001   | lfff        | ffff        | Z       | 2     |

| CLRW                                                                                                                                                                                                                                                                                                                                                                                        | -           | Clear W                      | 1       | 00    | 0001   | 0000        | XXXXXX      | z       |       |

| COMF                                                                                                                                                                                                                                                                                                                                                                                        | f, d        |                              | 1       | 00    | 1001   | dfff        | ffff        | z       | 1,2   |

|                                                                                                                                                                                                                                                                                                                                                                                             | f, d        | Decrement f                  | 1       | 00    | 0011   | dfff        | iiii        | Z       | 1,2   |

| DECFSZ                                                                                                                                                                                                                                                                                                                                                                                      | 1, d        | Decrement f, Skip if 0       | 1 (2)   | 00    | 1011   | dfff        | 1111        |         | 1,2,3 |

| INCF                                                                                                                                                                                                                                                                                                                                                                                        | ſ, d        | Increment f                  | 1       | 00    | 1010   | <b>dfff</b> | <u>tttt</u> | z       | 1,2   |

| INCFSZ                                                                                                                                                                                                                                                                                                                                                                                      | f, d        | Increment f, Skip if 0       | 1 (2)   | 00    | 1111   | dfff        | ffff        |         | 1,2,3 |

| IORWF                                                                                                                                                                                                                                                                                                                                                                                       | f, d        | Inclusive OR W with f        | 1       | 00    | 0100   | dfff        | ffff        | Z       | 1,2   |

| MOVF                                                                                                                                                                                                                                                                                                                                                                                        | f, d        | Move f                       | 1       | 00    | 1000   | dfff        | IIII        | Z       | 1,2   |

| MOVWF                                                                                                                                                                                                                                                                                                                                                                                       | f           | Move W to f                  | 1       | 00    | 0000   | 1111        | 1111        |         |       |

| NOP                                                                                                                                                                                                                                                                                                                                                                                         | *           | No Operation                 | 1       | 00    | 0000   | 0)000       | 0000        | ]       |       |

| RLF                                                                                                                                                                                                                                                                                                                                                                                         | f, d        | Rotate Left f through Carry  | 1       | 00    | 1101   | dfff        | ffff        | C       | 1,2   |

| RRF                                                                                                                                                                                                                                                                                                                                                                                         | f, d        | Rotate Right f through Carry | 1       | 00    | 1100   | dfff        | 1111        | l c     | 1.2   |

| SUBWF                                                                                                                                                                                                                                                                                                                                                                                       | t d         |                              | 1       | 00    | 0010   | dfff        | 1111        | C.DC.Z  | 1,2   |

| SWAPF                                                                                                                                                                                                                                                                                                                                                                                       | f, d        | Swap nibbles in f            | 1       | 00    | 1110   | attt        | 1111        |         | 1,2   |

| XORWF                                                                                                                                                                                                                                                                                                                                                                                       | f, d        | Exclusive OR W with f        | 1       | 00    | 0110   | attt        | iiii        | z       | 1,2   |

|                                                                                                                                                                                                                                                                                                                                                                                             |             | BIT-ORIENTED FILE REGIST     | ER OPER | ATION | 15     |             |             | <b></b> |       |

| BCF                                                                                                                                                                                                                                                                                                                                                                                         | f, b        | Bit Clear f                  | 1       | 01    | 00bb   | bfff        | ffff        |         | 1,2   |

| BSF                                                                                                                                                                                                                                                                                                                                                                                         | f, b        | Bit Set f                    | 1       | 01    | 01bb   | bfff        | ffff        |         | 1.2   |

| BTFSC                                                                                                                                                                                                                                                                                                                                                                                       | f, b        | Bit Test f, Skip if Clear    | 1 (2)   | 01    | 10bb   | bfff        | 1111        | 1       | 3     |

| BTFSS                                                                                                                                                                                                                                                                                                                                                                                       | f, b        | Bit Test f, Skip if Set      | 1 (2)   | 01    | 11bb   | bfff        | 1111        |         | 3     |

|                                                                                                                                                                                                                                                                                                                                                                                             | -           | LITERAL AND CONTROL          | OPERAT  | IONS  |        |             | 1           |         |       |

| ADDLW                                                                                                                                                                                                                                                                                                                                                                                       | k           | Add literal and W            | 1       | 11    | 111x   | kkkk        | kkkk        | C,DC,Z  |       |

| ANDLW                                                                                                                                                                                                                                                                                                                                                                                       | k           | AND literal with W           | 1       | 11    | 1001   | kkkk        | kkkk        | Z       |       |

| CALL                                                                                                                                                                                                                                                                                                                                                                                        | ĸ           | Call subroutine              | 2       | 10    | 0kkk   | kkkk        | kkkk        |         |       |

| CLRWDT                                                                                                                                                                                                                                                                                                                                                                                      | -           | Clear Watchdog Timer         | 1       | 00    | 0000   | 0110        | 0100        | TO,PD   |       |

| GOTO                                                                                                                                                                                                                                                                                                                                                                                        | ĸ           | Go to address                | 2       | 10    | 1kkk   | kkkk        | kkkk        | ł       |       |

| IORLW                                                                                                                                                                                                                                                                                                                                                                                       | k           | Inclusive OR literal with W  | 1       | 11    | 1000   | kkkk        | kkkk        | z       |       |

| MOVLW                                                                                                                                                                                                                                                                                                                                                                                       | ĸ           | Move literal to W            | 1       | 11    | 00xx   | kkkk        | kkkk        |         |       |

| RETFIE                                                                                                                                                                                                                                                                                                                                                                                      | -           | Return from interrupt        | 2       | 00    | 0000   | 0000        | 1001        |         |       |

| RETLW                                                                                                                                                                                                                                                                                                                                                                                       | k           | Return with literal in W     | 2       | 11    | 01xx   | kkkk        | kkkk        |         |       |

| RETURN                                                                                                                                                                                                                                                                                                                                                                                      | -           | Return from Subroutine       | 2       | 00    | 0000   | 0000        | 1000        |         |       |

| SLEEP                                                                                                                                                                                                                                                                                                                                                                                       | -           | Go into standby mode         | 1       | 00    | 0000   | 0110        | 0011        | TO,PD   |       |

| SUBLW                                                                                                                                                                                                                                                                                                                                                                                       | k           | Subtract W from literal      | 1       | 11    | 110x   | kkkk        | kkkk        | C.DC.Z  |       |

| XORLW                                                                                                                                                                                                                                                                                                                                                                                       | ĸ           | Exclusive OR literal with W  | 1       | 11    | 1010   | kkkk        |             | Z       |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is

executed as a NOP.

.

.

# **Pin Diagram**

#### SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| R/W-0 | R/W-0 | R-0 | R-0    | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|--------|-----|-----|-----|-------|

| SMP   | CKE   | D/Ā | Р      | S   | R/W | UA  | BF    |

| bit 7 |       | •   | ****** |     | ·   |     | bit 0 |

SMP: Sample bit

SPI Master mode:

1 = Input data sampled at end of data output time

0 = Input data sampled at middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in slave mode

In I<sup>2</sup>C Master or Slave mode:

1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)

0 = Slew rate control enabled for high speed mode (400 kHz)

CKE: SPI Clock Edge Select (Figure 9-2, Figure 9-3 and Figure 9-4)

SPI\_mode:

For CKP = 0

1 = Data transmitted on rising edge of SCK

0 = Data transmitted on falling edge of SCK

For CKP = 1

1 = Data transmitted on failing edge of SCK

0 = Data transmitted on rising edge of SCK

In I<sup>2</sup>C Master or Slave mode:

1 = Input levels conform to SMBus spec

0 =Input levels conform to I<sup>2</sup>C specs

D/A: Data/Address bit (I<sup>2</sup>C mode only)

1 = Indicates that the last byte received or transmitted was data

0 = Indicates that the last byte received or transmitted was address

P: STOP bit

(I<sup>2</sup>C mode only. This bil is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)

0 = STOP bit was not detected last

S: START bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)

0 = START bit was not detected last

RW: Read/Write bit Information (I<sup>2</sup>C mode only)

This bit holds the RAW bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit or not ACK bit.

In I<sup>2</sup>C Slave mode:

1 = Read

0 = Write

In J<sup>2</sup>C Master mode:

1 = Transmit is in progress

0 = Transmit is not in progress

Logical OR of this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode.

UA: Update Address (10-bit I<sup>2</sup>C mode only)

1 = indicates that the user needs to update the address in the SSPADD register

0 = Address does not need to be updated

BF: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes):

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only):

1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full

0 = Data transmit complete (does not include the ACK and STOP bits), SSPBUF is empty

· .

| R/W-0                                                                                                                      | R/W-0                                                                                                                         | R/W-0                                                                                                | R/W-0                                                                         | R/W-0                                                            | R/W-0                                        | R/W-0                         | R/W-0                       |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------|-------------------------------|-----------------------------|

| WCOL                                                                                                                       | SSPOV                                                                                                                         | SSPEN                                                                                                | СКР                                                                           | SSPM3                                                            | SSPM2                                        | SSPM1                         | SSPMO                       |

| t7                                                                                                                         |                                                                                                                               |                                                                                                      |                                                                               |                                                                  |                                              |                               | bit 0                       |

| laster mod<br>= A write t<br>= No collis<br>lave mode                                                                      | io SSPBUF wa<br>ion<br>Fregister is w<br>)                                                                                    | etect bit<br>as attempted r<br>rritten while st                                                      |                                                                               |                                                                  |                                              | be cleared in                 |                             |

|                                                                                                                            |                                                                                                                               | w Indicator bi                                                                                       | ł                                                                             |                                                                  |                                              |                               |                             |

| mode, ti<br>mode, ti<br>(Must bi<br>= No over<br><u>n I<sup>2</sup>C mode</u><br>= A byte is                               | yte is received<br>he user must i<br>he overflow bi<br>e cleared in so<br>flow<br><u>:</u><br>s received whi<br>Must be clear | i while SSPBL<br>read the SSPI<br>t is not set, sii<br>oftware.)<br>le the SSPBU<br>ed in software   | BUF, even if o<br>nce each ope<br>F is holding th                             | only transmitti<br>ration is initia                              | ng data, to av<br>ted by writing             | old overflows<br>to the SSPBI | . In Master<br>UF register. |

|                                                                                                                            |                                                                                                                               | rial Port Enab                                                                                       | la hit                                                                        |                                                                  |                                              |                               | A.                          |

| = Enables<br>= Disables<br>1 <sup>2</sup> C mode<br>Vhen enabl<br>= Enables                                                | ed, these pins<br>serial port an<br>s serial port ar<br>,<br>ed, these pins<br>the serial por                                 | a must be prop<br>d configures t<br>d configures<br>and configures<br>and configures<br>d configures | SCK, SDO, S<br>these pins as<br>perty configur<br>res the SDA a               | DI, and SS as<br>I/O port pins<br>ed as input of<br>and SCL pins | s the source of<br>r output<br>as the source |                               |                             |

| KP: Clock                                                                                                                  | Polarity Selec                                                                                                                | t bit                                                                                                |                                                                               |                                                                  |                                              |                               |                             |

| ) = Idle stat<br>n 1 <sup>2</sup> C Slave<br>CK release<br>L = Enable (                                                    | e for clock is a<br>e for clock is a<br><u>mode</u> :<br>e control<br>clock<br>ock low (clock<br><u>er mode:</u>              |                                                                                                      | ed to ensure :                                                                | data setup tin                                                   | ne.)                                         |                               |                             |

| 000 = SPI<br>001 = SPI<br>010 = SPI<br>011 = SPI<br>100 = SPI<br>101 = SPI<br>$110 = I^2C$<br>$111 = I^2C$<br>$000 = I^2C$ | Master mode<br>Master mode<br>Master mode<br>Slave mode,<br>Slave mode,<br>Slave mode,<br>Slave mode,<br>Slave mode,          | IO-bit address<br>clock = Fosc                                                                       | 2/4<br>5/16<br>5/64<br>2 output/2<br>55 pin co<br>55 pin co<br>1/ (4 * (SSPA) | ntrol enabled<br>ntrol disabled<br>DD+1))                        | l. SS can be u                               | used as I/O pi                | ο.                          |

## PIC16F877/876 REGISTER FILE MAP

| ļ                             | File<br>Address | ,                    | File<br>Address |                               | File<br>Address |                               | Fille<br>Addre: |

|-------------------------------|-----------------|----------------------|-----------------|-------------------------------|-----------------|-------------------------------|-----------------|

| Indirect addr. <sup>(*)</sup> | 00h             | Indirect addr.(*)    | 80h             | Indirect addr. <sup>(*)</sup> | 100h            | Indirect addr. <sup>(*)</sup> | 1801            |

| TMR0                          | 01h             | OPTION REG           | 81h             | TMR0                          | 101h            | OPTION_REG                    | 1811            |

| PCL                           | 02h             | PCL                  | 82h             | PCL                           | 102h            | PCL                           | 1821            |

| STATUS                        | 03h             | STATUS               | 83h             | STATUS                        | 103h            | STATUS                        | 1831            |

| FSR                           | 04h             | FSR                  | 84h             | FSR                           | 104h            | FSR                           | 1841            |

| PORTA                         | 05h             | TRISA                | 85h             |                               | 105h            |                               | 185             |

| PORTB                         | 06h             | TRISB                | 86h             | PORTB                         | 106h            | TRISB                         | 1861            |

| PORTC                         | 07h             | TRISC                | 87h             |                               | 107h            |                               | 1871            |

| PORTD <sup>(1)</sup>          | 08h             | TRISD <sup>(1)</sup> | 88h             |                               | 108h            |                               | 188             |

| PORTE <sup>(1)</sup>          | 09h             | TRISE <sup>(1)</sup> | 89h             |                               | 109h            |                               | 189             |

| PCLATH                        | QAh             | PCLATH               | 8Ah             | PCLATH                        | 10Ah            | PCLATH                        | 18A             |

| INTCON                        | 0Bh             | INTCON               | 8Bh             | INTCON                        | 108h            | INTCON                        | 18B             |

| PIR1                          | 0Ch             | PIE1                 | 8Ch             | EEDATA                        | 10Ch            | EECON1                        | 18C             |

| PIR2                          | 0Dh             | PIE2                 | 8Dh             | EEADR                         | 10Dh            | EECON2                        | 18D             |

| TMR1L                         | 0Eh             | PCON                 | 8Eh             | EEDATH                        | 10Eh            | Reserved                      | 18E             |

| TMR1H                         | OFh             |                      | 8Fh             | EEADRH                        | 10Fh            | RESERVED                      | 18F1            |

| T1CON                         | 10h             |                      | 90h             |                               | 110h 🗠          |                               | 190ł            |

| TMR2                          | 11h             | SSPCON2              | 91h             |                               | 111h            |                               | 1911            |

| T2CON                         | 12h             | PR2                  | 92h             |                               | 112h            |                               | 1921            |

| SSPBUF                        | 13h             | SSPADD               | 93h             |                               | 113h            |                               | 193             |

| SSPCON                        | 14h             | SSPSTAT              | 94h             |                               | 114h            |                               | 1941            |

| CCPR1L                        | 15h             |                      | 95h             |                               | 115h            |                               | 1951            |

| CCPR1H                        | 16h             |                      | 96h             |                               | 116h            |                               | 196             |

| CCP1CON                       | 17h             |                      | 97h             | General<br>Purpose            | 117h            | General<br>Purpose            | 1971            |

| RCSTA                         | 18h             | TXSTA                | 98h             | Register                      | 118h            | Register                      | 1981            |

| TXREG                         | 19h             | SPBRG                | 99h             | 16 Bytes                      | 119h            | 16 Bytes                      | 1991            |

| RCREG                         | 1Ah             | and the rest         | 9Ah             |                               | 11Ah            |                               | 19A             |

| CCPR2L                        | 1Bh             |                      | 9Bh             | 1                             | 118h            |                               | 19B             |

| CCPR2H                        | 1Ch             |                      | 9Ch             |                               | 11Ch            |                               | 1903            |

| CCP2CON                       | 1Dh             |                      | 9Dh             |                               | 11Dh            |                               | 19D             |

| ADRESH                        | 1Eh             | ADRESL               | 9Eh             |                               | 11Eh            |                               | 19E             |

| ADCON0                        | 1Fh             | ADCON1               | 9Fh             |                               | 11Fh            |                               | 19F1            |

|                               | 20h             |                      | A0h             |                               | 120h            |                               | 1A0             |

| General                       |                 | General              |                 | General                       |                 | General                       |                 |

| Purpose<br>Register           |                 | Purpose<br>Register  |                 | Purpose<br>Register           |                 | Purpose<br>Register           |                 |

| -                             |                 | 80 Bytes             |                 | 80 Bytes                      |                 | 80 Bytes                      | 400             |

| 96 Bytes                      |                 |                      | EFh             |                               | 16Fh            |                               | 1EF             |

|                               |                 | accesses             | FOh             | accesses                      | 170h            | accesses                      | 1F0             |

|                               | 7Fh             | 70h-7Fh              | FFh             | 70h-7Fh                       | 17Fh            | 70h - 7Fh                     | 1FF             |

| Bank 0                        | 75.0            | Bank 1               | i FFN           | Bank 2                        | 1 2 5 58        | Bank 3                        | 10.1.1          |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

Note 1: These registers are not implemented on the PIC16F876. 2: These registers are reserved, maintain these registers clear.

### ADCON0 REGISTER (ADDRESS: 1Fh)

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0   | R/W-0 |

|-------|-------|-------|-------|-------|---------|-------|-------|

| ADCS1 | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE | ***** | ADON  |

| bit 7 |       |       |       |       |         |       | bit 0 |

ADCS1: ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

, ·

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from the internal A/D module RC oscillator)

CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (RA0/AN0)

001 = channel 1, (RA1/AN1)

010 = channel 2, (RA2/AN2)

011 = channel 3, (RA3/AN3)

100 = channel 4, (RA5/AN4)

101 = channel 5, (RE0/AN5)<sup>(1)</sup>

110 = channel 6, (RE1/AN6)<sup>(1)</sup>

111 = channel 7, (RE2/AN7)<sup>(1)</sup>

GO/DONE: A/D Conversion Status bit

If ADON = 1:

1 = A/D conversion in progress (setting this bit starts the A/D conversion)

0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)

Unimplemented: Read as '0'

ADON: A/D On bit

1 = A/D converter module is operating

0 = A/D converter module is shut-off and consumes no operating current

### ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0                                     | R/W-0 | U-0           | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-----------------------------------------|-------|---------------|-------|-------|-------|-------|--|

| ADFM  | 1000 ( <u>114</u> /1554)<br>2000 (1190) |       | Carlins State | PCFG3 | PCFG2 | PCFG1 | PCFG0 |  |

| bit 7 |                                         |       |               |       |       |       | bit 0 |  |

ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

Unimplemented: Read as '0'

• •

PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | ANG <sup>(1)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF-                   | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------------------------|------------------------------|

| 0000            | Α                         | A                         | A                         | Α          | A          | A          | A          | A          | VDD   | Vss                     | 8/0                          |

| 0001            | A                         | A                         | A                         | Α          | VREF+      | A          | Α          | A          | RA3   | Vss                     | 7/1                          |

| 0010            | D                         | D                         | D                         | Α          | Α          | A          | A          | A          | VDD   | Vss                     | 5/0                          |

| 0011            | D                         | D                         | D                         | A          | VREF+      | A          | Α          | Α          | RA3   | Vss                     | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | A          | D          | A          | A          | VDD   | <ul> <li>Vss</li> </ul> | 3/0                          |

| 0101            | D                         | D                         | D                         | D          | VREF+      | D          | A          | A          | RA3   | Vss                     | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | VDD   | Vss                     | 0/0                          |

| 1000            | A                         | A                         | Α                         | Α          | VREF+      | VREF-      | A          | A          | RA3   | RA2                     | 6/2                          |

| 1001            | D                         | D                         | A                         | Α          | A          | A          | A          | Α          | VDD   | Vss                     | 6/0                          |

| 1010            | D                         | D                         | Α                         | Α          | VREF+      | A          | Α          | A          | RA3   | Vss                     | 5/1                          |

| 1011            | D                         | D                         | A                         | Α          | VREF+      | VREF-      | A          | A          | RA3   | RA2                     | 4/2                          |

| 1100            | D                         | D                         | D                         | A          | VREF+      | VREF-      | Α          | A          | RA3   | RA2                     | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | A          | A          | RA3   | RA2                     | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | Ð          | D          | D          | A          | VDD   | Vss                     | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | VREF-      | D          | A          | RA3   | RA2                     | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |