# UNIVERSITY OF SWAZILAND MAIN EXAMINATION, SECOND SEMESTER MAY 2017

## FACULTY OF SCIENCE AND ENGINEERING

## DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

TITLE OF PAPER: MICROCONTROLLERS AND MICROCOMPUTER SYSTEMS COURSE CODE: EE423

TIME ALLOWED: THREE HOURS

## **INSTRUCTIONS:**

÷ 4.

- 1. There are five questions in this paper. Answer any FOUR questions. Each question carries 25 marks.

- 2. If you think not enough data has been given in any question, you may assume any reasonable values stating your assumptions in each case.

# THIS PAPER SHOULD NOT BE OPENED UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR

## THIS PAPER CONTAINS SIX (6) PAGES INCLUDING THIS PAGE

## **QUESTION ONE (25 marks)**

1

4

(a) (i) State the memory areas available and their usage in PIC16F84A.

(3 marks)

(ii) Identify the architecture used in PIC microcontrollers and state why this architecture is more faster.

(3 marks)

- (iii) How do you describe a microprocessor based system and a microcontroller based system?

(3 marks)

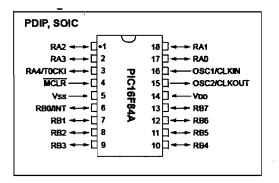

- (iv) Indicate the peripheral modules available in PIC 16F84A and PIC 16F877.

(2 marks)

(b) Consider the segment of a program shown in Figure-Q1 written for PIC16F84A.

| bsf   | 03,5        |

|-------|-------------|

| movlw | b'01000110' |

| movwf | 06          |

| movwf | 01          |

| bcf   | 03,5        |

Figure-Q1

(i) Explain all the statements shown in Figure-Q1.

(4 marks)

(ii) Write the first three code lines in Figure-Q1 with machine code.

(3 marks)

(iii) In an application it is required to use timer TMR0 overflow occurring in every 5ms. Select giving justification a crystal from the following list, for the clock oscillator that will give a minimum timing error. What is the percentage error in timing? Modify the code in Figure-Q1 only to accommodate your selection.

The crystals available are,

1MHz, 2.457MHz, 3.579MHz 4MHz.

(7 marks)

## **QUESTION TWO (25 marks)**

١,

A simple farm irrigation system is designed based on a 16F84A microcontroller. The system consists with a soil moisture sensing unit, rain sensor, water tank with a level sensing unit, water pump to fill the tank and a water sprinkler system. Following is a list of TTL compatible signals to be handled.

| <u>Signal</u> | Description                                                                                                                                                    |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| М             | Soil moisture sensing unit output. Returns logic '1' if the                                                                                                    |

|               | moisture is lower than the set limit.                                                                                                                          |

| R             | Rain sensor output. Returns logic '1' if the rain is present.                                                                                                  |

| W             | Output of the water level sensor unit of the water tank with incorporated hysteresis. Returns logic '1' if the water level is <u>lower</u> than the set limit. |

| Р             | Control signal of the water pump which fills the tank. Logic '1' activates the pump.                                                                           |

| S             | Control signal for the water sprinkler system. Logic '1' activates it.                                                                                         |

(i) Draw a circuit diagram for this system showing all signal interconnections with the pin numbers of the microcontroller. You may omit the components required for the clock oscillator. Sensors and the controlled components can be shown as blocks.

(5 marks)

Suggest the control logic that you are going to implement by the microcontroller program.

(7 marks)

(iii) Draw a flowchart for the microcontroller program based on (ii) above.

(9 marks)

(iv) Using assembly instructions show how you are going to configure the ports as required.

(4 marks)

## **QUESTION THREE (25 marks)**

. N

A block of assembly code program written for 16F84A is shown in Figure-Q3. For the clock oscillator, a 8MHz crystal is used and the supply is +5V. Assume that the variables P, M and N have been already defined with other special function registers.

| start<br>begin          | org o<br>goto start<br>-<br>-<br>-<br>org 64h<br>bsf status, 5<br>movlw b'01010101'<br>tris portA<br>movlw b'10101010'<br>tris portB<br>movlw b'00000001'<br>option<br>bcf status, 5<br>clrf portB<br>movlw .1<br>movwf P<br>movwf M<br>movwf N | movf P, w<br>sublw .5<br>btfsc status, 2<br>goto begin<br>incf P,1<br>movf P, w<br>movwf N<br>goto lab-1<br>break clrf tmr0<br>loop movf tmr0, w<br>sublw .82<br>btfss status, 2<br>goto loop<br>return |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lab-1<br>lab-2<br>lab-3 | bsf portB, 0<br>call break<br>decfsz N, 1<br>goto lab-2<br>bcf portB, 0<br>call break<br>decfsz M, 1<br>goto lab-3                                                                                                                              |                                                                                                                                                                                                         |

|                         | Figure                                                                                                                                                                                                                                          | <br>>-03                                                                                                                                                                                                |

- (i) From what memory location the actual code is written in the program memory of the Microcontroller? (2 marks)

- (ii) Identify the port pin to which the output of the program is assigned.

(2 marks)

(iii) Find and copy the subroutine part of the code and evaluate as accurate as possible the time taken to execute it.

(6 marks)

(iv) Build a complete flow chart to describe the function of the program.

(7 marks)

(v) Draw the resulting output waveform for a period of 5ms after the execution of the program from 'begin .....' statement. You need to mark the voltage and time information supported with calculations where necessary.

(8 marks)

### **QUESTION FOUR (25 marks)**

• •

(a) State the sources that can make an interrupt on a 16F84A microcontroller.

(3 marks)

- (b) A 16F84A is considered for the following.

- (i) 'Task one' and 'Task two' are two different assembly code blocks. On low to high transition of an interrupt signal from an external device, 'Task one' needs to be executed. When the interrupt signal moves from high to low, 'Task two' needs to be executed. Select a port pin for the connection of interrupt signal. Show the configurations of the registers involved. Assume that no other types of interrupts are used.

- (ii) Show the contents of the registers which are effected after an interrupt mentioned in (b)(i) above.

(3 marks)

(5 marks)

(iii) Draw a flow chart with enough details to show the servicing of interrupts mentioned in (b)(i) above.

(7 marks)

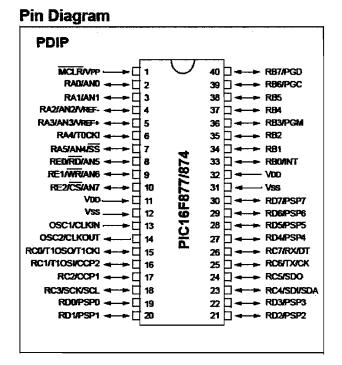

- (c) A PIC 16F877 microcontroller is considered for the following.

- (i) When using its Analog to Digital Converter (ADC), it is required to configure it to have external voltage reference, four analog inputs, a clock source of  $\frac{fosc}{2}$ . If the input channel 1 is selected and ADC turned on but not started converting, show the settings of the relevant registers. When the conversion is started and running, what are the changes in these registers? State your assumptions if there are any. (4 marks)

- (ii) If an 8MHz crystal oscillator is to be used, select a suitable option for ADCS1 and ADCS0 bits in the ADCON0 register justifying the answer.

(3 marks)

## **QUESTION FIVE (25 marks)**

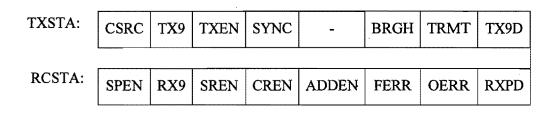

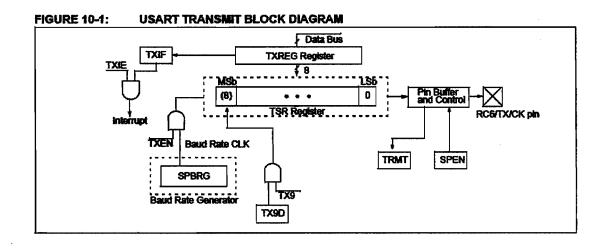

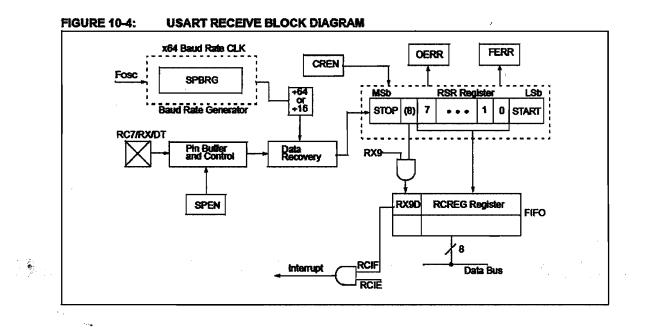

(a) A 16F877 is required to be connected to another device equipped with an USART interface. Communication is done full duplex and asynchronous with a baud rate of 9600Hz. A 8MHz crystal oscillator is used and 8 bit data transfer is assumed.

(i) Show how the 16F877 can be connected to the device USART interface. Any known pin numbers

and pin names related to USART must be clearly marked.

(ii) Write the bit configuration of the registers TXSTA, SPBRG and RCSTA assuming high speed option.

You may use,  $BR = \frac{F_{osc}}{16(X+1)}$  with usual notation.

(9 marks)

(iii) State when and where new data to be transmitted must be loaded and new data received can be recovered.

(4 marks)

(b) A device that can transfer data at a maximum rate of 125kHz through SPI needs to be interfaced with a 16F877. Assume that the microcontroller is running on a 8MHz crystal oscillator.

If the microcontroller is configured for SPI mode to connect with the device, show the settings of the SSPCON, SSPSTAT and any other register involved. It must include the settings for the zero idle state of clock, data sampling at the middle of the bit period and the data transfers are on the rising edge of clock.

(10 marks)

## PIC 16F84A

1

| File Addre | 55                                              | F                                 | ile Address |

|------------|-------------------------------------------------|-----------------------------------|-------------|

| 00h        | Indirect addr. <sup>(1)</sup>                   | Indirect addr. <sup>(1)</sup>     | 80h         |

| Oth        | TMR0                                            | OPTION_REG                        | 81h         |

| 02h        | PCL                                             | PCL                               | 82h         |

| 03h        | STATUS                                          | STATUS                            | 83h         |

| 04h        | FSR                                             | FSR                               | 84h         |

| 05h        | PORTA                                           | TRISA                             | 85h         |

| 06h        | PORTB                                           | TRISB                             | 86h         |

| 07h        |                                                 |                                   | 87h         |

| 08h        | EEDATA                                          | EECON1                            | 88h         |

| 09h        | EEADR                                           | EECON2 <sup>(1)</sup>             | 89h         |

| 0Ah        | PCLATH                                          | PCLATH                            | 8Ah         |

| OBh        | INTCON                                          | INTCON                            | 88h         |

| DCh        | 68<br>General<br>Purpose<br>Registers<br>(SRAM) | Mapped<br>(accesses)<br>in Bank 0 | 8Ch         |

| 4Fh<br>50h |                                                 |                                   | CFh<br>D0h  |

### STATUS REGISTER (ADDRESS 03h, 83h)

| R/W-0 | R/W-0 | R/W-0 | R-1 | R-1 | R/W-x | R/W-x | R/W-x |

|-------|-------|-------|-----|-----|-------|-------|-------|

| IRP   | RP1   | RP0   | TO  | PD  | Z     | DC    | С     |

| bit 7 |       |       |     |     | •     |       | bit O |

Unimplemented: Maintain as '0'

RP0: Register Bank Select bits (used for direct addressing)

01 = Bank 1 (80h - FFh)

00 = Bank 0 (00h - 7Fh)

TO: Time-out bit

1 = After power-up, CLRWDT instruction, or SLEEP instruction

0 = A WDT time-out occurred

PD: Power-down bit

1 = After power-up or by the CLRWDT instruction

0 = By execution of the SLEEP instruction

Z: Zero bit

1 = The result of an arithmetic or logic operation is zero

0 = The result of an arithmetic or logic operation is not zero

DC: Digit carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed)

1 = A carry-out from the 4th low order bit of the result occurred

0 = No carry-out from the 4th low order bit of the result

C: Carry/Dorrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions) (for borrow, the polarity is reversed)

1 = A carry-out from the Most Significant bit of the result occurred

0 = No carry-out from the Most Significant bit of the result occurred

Note: A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.

Data Page 1 of 10

## PIC 16F84A

### OPTION REGISTER (ADDRESS 81h)

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       | -     | -     |       |       | bit 0 |

RBPU: PORTB Pull-up Enable bit

1 = PORTB pull-ups are disabled

0 = PORTB pull-ups are enabled by individual port latch values

INTEDG: Interrupt Edge Select bit

1 = Interrupt on rising edge of RB0/INT pin

0 = Interrupt on falling edge of RB0/INT pin

TOCS: TMRD Clock Source Select bit

1 = Transition on RA4/T0CKI pin

0 = Internal instruction cycle clock (CLKOUT)

TOSE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on RA4/T0CKI pin

0 = Increment on low-to-high transition on RA4/TOCKI pin

PSA: Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

PS2:PS0: Prescaler Rate Select bits

Bit Value TMR0 Rate WDT Rate

| 000 | 1:2     | 1:1     |

|-----|---------|---------|

| 001 | 1:4     | 1:2     |

| 010 | 1:8     | 1:4     |

| 011 | 1:16    | 1:8     |

| 100 | 1:32    | 1:16    |

| 101 | 1:64    | 1:32    |

| 110 | 1 : 128 | 1:64    |

| 111 | 1:256   | 1 : 128 |

|     |         |         |

### INTCON REGISTER (ADDRESS 0Bh, 8Bh)

| R/W-0 | R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | EEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTE  | RBIF  |

| bit 7 | •     |       |       |       |       |       | bit 0 |

GIE: Global Interrupt Enable bit

1 = Enables all unmasked interrupts

0 = Disables all interrupts

EEIE: EE Write Complete Interrupt Enable bit

1 = Enables the EE Write Complete interrupts

0 = Disables the EE Write Complete interrupt

TOLE: TMR0 Overflow Interrupt Enable bit

1 = Enables the TMR0 interrupt

0 = Disables the TMR0 interrupt

INTE: RB0/INT External Interrupt Enable bit 1 = Enables the RB0/INT external interrupt

0 = Disables the RB0/INT external interrupt

RBIE: RB Port Change Interrupt Enable bit

1 = Enables the RB port change interrupt

0 = Disables the RB port change interrupt

T0IF: TMR0 Overflow Interrupt Flag bit

1 = TMR0 register has overflowed (must be cleared in software)

o = TMR0 register did not overflow

INTF: RB0/INT External Interrupt Flag bit

1 = The RB0/INT external interrupt occurred (must be cleared in software)

0 = The RB0/INT external interrupt did not occur

RBIF: RB Port Change Interrupt Flag bit

1 = At least one of the RB7:RB4 pins changed state (must be cleared in software)

0 = None of the RB7:RB4 pins have changed state

Data Page 2 of 10

## 16F84A and 16F877

۰.

| Mnem   | onic, | Provedu dia a                | Overlag  |       | 14-Bit | Opcode | )     | Status   | Notes |

|--------|-------|------------------------------|----------|-------|--------|--------|-------|----------|-------|

| Opera  | ands  | Description                  | Cycles   | MSD   |        |        | LSb   | Affected | NOURS |

|        |       | BYTE-ORIENTED FILE REGI      | STER OPE | RATIC | NS     |        |       |          |       |

| ADDWF  | f, d  | Add W and f                  | 1        | 00    | 0111   | dfff   | ffff  | C,DC,Z   | 1,2   |

| ANDWF  | f, d  | AND W with f                 | 1        | 00    | 0101   | dfff   | 1111  | Z        | 1,2   |

| CLRF   | f     | Clear f                      | 1        | 00    | 0001   | lfff   | ffff  | Z        | 2     |

| CLRW   | -     | Clear W                      | 1        | 00    | 0001   | 0,000  | XXXXX | z        |       |

| COMF   | f, d  | Complement f                 | 1        | 00    | 1001   |        | 1111  | Z        | 1,2   |

| DECF   | f, d  | Decrement f                  | 1        | 00    |        | dfff   | -++-  | Z        | 1,2   |

| DECFSZ | f, đ  | Decrement f, Skip if 0       | 1 (2)    | 00    | 1011   | dfff   | iiii  |          | 1,2,3 |

| INCF   | f, d  | Increment f                  | 1        | 00    |        | dfff   |       | Z        | 1,2   |

| INCFSZ | f, d  | Increment f, Skip if 0       | 1 (2)    | 00    | 1111   | dfff   | IIII  |          | 1,2,3 |

| IORWF  | f, d  | Inclusive OR W with f        | 1        | 00    | 0100   |        | 1111  | Z        | 1,2   |

| MOVF   | f, d  | Move f                       | 1        | 00    | 1000   | dfff   | IIII  | Z        | 1,2   |

| MOVWF  | f     | Move W to f                  | 1        | 00    | 0000   | lfff   | ffff  |          |       |

| NOP    | -     | No Operation                 | 1        | 00    | 0000   | 0,000  | 0000  |          |       |

| RLF    | f, d  | Rotate Left f through Carry  | 1        | 00    | 1101   | dfff   | ffff  | C        | 1,2   |

| RRF    | f, d  | Rotate Right f through Carry | 1        | 00    | 1100   | dfff   | ffff  | C C      | 1,2   |

| SUBWF  | f, d  | Subtract W from f            | 1        | 00    | 0010   | dfff   | IIII  | C,DC,Z   | 1,2   |

| SWAPF  | f, d  | Swap nibbles in f            | 1        | 00    | 1110   | dfff   | IIII  |          | 1,2   |

| XORWF  | ſ, d  | Exclusive OR W with f        | 1        | 00    | 0110   | dfff   | 1111  | Z        | 1,2   |

|        |       | BIT-ORIENTED FILE REGIS      | TER OPEI | RATIO | NS     |        |       |          |       |

| BCF    | f, b  | Bit Clear f                  | 1        | 01    | did 00 | bfff   | tttt  |          | 1,2   |

| BSF    | ſ, b  | Bit Set f                    | 1        | 01    | 01bb   | bfff   | iiii  |          | 1,2   |

| BTFSC  | f, D  | Bit Test f, Skip if Clear    | 1 (2)    | 01    | 1000   | bfff   | iiii  |          | 3     |

| BTFSS  | f, b  | Bit Test f, Skip if Set      | 1 (2)    | 01    | 11bb   | þfff   | ffff  |          | 3     |

|        |       | LITERAL AND CONTROL          | OPERAT   | IONS  |        |        |       |          |       |

| ADDLW  | ĸ     | Add literal and W            | 1 1      | 11    |        |        | kkkk  | C,DC,Z   |       |

| ANDLW  | ĸ     | AND literal with W           | 1        | 11    | 1001   | kkkk   | kkkk  | Z        |       |

| CALL   | ĸ     | Call subroutine              | 2        | 10    | 0kkk   | kkkk   | kkkk  |          |       |

| CLRWDT | -     | Clear Watchdog Timer         | 1        | 00    | 0000   | 0110   | 0100  | TO,PD    |       |

| GOTO   | ĸ     | Go to address                | 2        | 10    | 1kkk   | kkk    | kkkk  |          |       |

| IORLW  | ĸ     | Inclusive OR literal with W  | 1        | 11    | 1000   | kkk    | kkkk  | Z        |       |

| MOVLW  | ĸ     | Move literal to W            | 1        | 11    | 00xx   | kkkk   | kkkk  |          |       |

| RETFIE | -     | Return from interrupt        | 2        | 00    | 0000   | 0000   | 1001  |          |       |

| RETLW  | k     | Return with literal in W     | 2        | 11    | 01.xx  | kkk    | kkkk  |          |       |

| RETURN | -     | Return from Subroutine       | 2        | 00    | 0000   | 0000   | 1000  |          |       |

| SLEEP  | -     | Go into standby mode         | 1        | 00    | 0000   | 0110   | 0011  | TO,PD    | I     |

| SUBLW  | ĸ     | Subtract W from literal      | 1        | 11    | 110x   | kkk    | kkkk  | C,DC,Z   |       |

| XORLW  | k     | Exclusive OR literal with W  | 1        | 11    | 1010   | kkkk   | kxxk  | Z        |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVT PORTE, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared If assigned to the Timer0 Module.

If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is

executed as a NOP.

Data Page 3 of 10

.

N. . .

Data Page 4 of 10

### SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (ADDRESS: 94h)

| SMP   | CKE | D/Ā | Р | S | RAW      | UA | BF    |   |

|-------|-----|-----|---|---|----------|----|-------|---|

| bit 7 |     |     |   |   | <b>-</b> |    | bit 0 | ŀ |

SMP: Sample bit

SPI Master mode:

1 = input data sampled at end of data output time

0 = Input data sampled at middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in slave mode

In I<sup>2</sup>C Master or Slave mode:

1 = Slew rate control disabled for standard speed mode (100 kHz and 1 MHz)

0 = Slew rate control enabled for high speed mode (400 kHz)

CKE: SPI Clock Edge Select (Figure 9-2, Figure 9-3 and Figure 9-4)

SPI mode:

For CKP = 0

1 = Data transmitted on rising edge of SCK

0 = Data transmitted on falling edge of SCK

For CKP = 1

1 = Data transmitted on failing edge of SCK

0 = Data transmitted on rising edge of SCK

In I<sup>2</sup>C Master or Slave mode:

1 = input levels conform to SMBus spec

0 = Input levels conform to I<sup>2</sup>C specs

D/A: Data/Address bit (I<sup>2</sup>C mode only)

1 = Indicates that the last byte received or transmitted was data

0 = indicates that the last byte received or transmitted was address

P: STOP bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a STOP bit has been detected last (this bit is '0' on RESET)

0 = STOP bit was not detected last

S: START bit

(I<sup>2</sup>C mode only. This bit is cleared when the MSSP module is disabled, SSPEN is cleared.)

1 = Indicates that a START bit has been detected last (this bit is '0' on RESET)

0 = START bit was not detected last

**R/W:** Read/Write bit Information (I<sup>2</sup>C mode only)

This bit holds the RAW bit information following the last address match. This bit is only valid from the address match to the next START bit, STOP bit or not ACK bit.

In I<sup>2</sup>C Slave mode:

1 = Read

0 = Write

2

In I<sup>2</sup>C Master mode:

1 = Transmit is in progress

0 = Transmit is not in progress

Logical OR of this bit with SEN, RSEN, PEN, RCEN, or ACKEN will indicate if the MSSP is in IDLE mode.

UA: Update Address (10-bit I<sup>2</sup>C mode only)

1 = Indicates that the user needs to update the address in the SSPADD register

0 = Address does not need to be updated

### BF: Buffer Full Status bit

Receive (SPI and I<sup>2</sup>C modes):

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

Transmit (I<sup>2</sup>C mode only):

1 = Data transmit in progress (does not include the ACK and STOP bits), SSPBUF is full

0 = Data transmit complete (does not include the ACK and STOP bits), SSPBUF is empty

Data Page 5 of 10

## SSPCON: SYNC SERIAL PORT CONTROL REGISTER (ADDRESS 14h)

| R/W-0 | R/W-0 | RAW-0 | R/W-0 | R.W-0 | R/W-0 | R/W-0 | R/W-0 | - |

|-------|-------|-------|-------|-------|-------|-------|-------|---|

| WCOL  | SSPOV | SSPEN | СКР   | SSPM3 | SSPM2 | SSPM1 | SSPM0 |   |

| bit 7 |       |       |       | •     |       |       | bit O | • |

### WCOL: Write Collision Detect bit

Master mode:

1 = A write to SSPBUF was attempted while the I2C conditions were not valid

### 0 = No collision

Slave mode:

- 1 = SSPBUF register is written while still transmitting the previous word (must be cleared in software)

- 0 = No collision

SSPOV: Receive Overflow Indicator bit

### In SPI mode:

- 1 = A new byte is received while SSPBUF holds previous data. Data in SSPSR is lost on overflow. In Slave mode, the user must read the SSPBUF, even if only transmitting data, to avoid overflows. In Master mode, the overflow bit is not set, since each operation is initiated by writing to the SSPBUF register. (Must be cleared in software.)

- 0 = No overflow

In I<sup>2</sup>C mode:

1 = A byte is received while the SSPBUF is holding the previous byte. SSPOV is a "don't care" in Transmit mode. (Must be cleared in software.)

### 0 = No overflow

### SSPEN: Synchronous Serial Port Enable bit

In SPI mode,

When enabled, these pins must be properly configured as input or output

1 = Enables serial port and configures SCK, SDO, SDI, and SS as the source of the serial port pins

0 = Disables serial port and configures these pins as I/O port pins

in I<sup>2</sup>C mode,

When enabled, these pins must be properly configured as input or output

1 = Enables the serial port and configures the SDA and SCL pins as the source of the serial port pins 0 = Disables serial port and configures these pins as I/O port pins

### CKP: Clock Polarity Select bit

In SPI mode:

1 = Idle state for clock is a high level

0 = Idle state for clock is a low level

### In I<sup>2</sup>C Slave mode:

SCK release control

1 = Enable clock

0 = Holds clock low (clock stretch). (Used to ensure data setup time.)

In I<sup>2</sup>C Master mode:

Unused in this mode

### SSPM3:SSPM0: Synchronous Serial Port Mode Select bits

0000 = SPI Master mode, clock = Fosc/4

0001 = SPI Master mode, clock = Fosc/16

0010 = SPI Master mode, clock = Fosc/64

0011 = SPI Master mode, clock = TMR2 output/2

0100 = SPI Stave mode, clock = SCK pin. SS pin control enabled.

0101 = SPI Slave mode, clock = SCK pin. SS pin control disabled. SS can be used as I/O pin.

0110 = I<sup>2</sup>C Slave mode, 7-bit address

$0111 = I^2C$  Slave mode, 10-bit address

1000 = I<sup>2</sup>C Master mode, clock = Fosc / (4 \* (SSPADD+1))

1011 = I<sup>2</sup>C Firmware Controlled Master mode (slave idle)

1110 =  $l^2$ C Firmware Controlled Master mode, 7-bit address with START and STOP bit interrupts enabled

1111 = I<sup>2</sup>C Firmware Controlled Master mode, 10-bit address with START and STOP bit interrupts enabled

1001, 1010, 1100, 1101 = Reserved

Data Page 6 of 10

## PIC16F877/876 REGISTER FILE MAP

| A                             | File<br>Vddness | ,                             | File<br>Address |                                       | File<br>Address |                               | File<br>Address |

|-------------------------------|-----------------|-------------------------------|-----------------|---------------------------------------|-----------------|-------------------------------|-----------------|

| Indirect addr. <sup>(*)</sup> | 00h             | Indirect addr. <sup>(*)</sup> | 80h             | Indirect addr. <sup>(*)</sup>         | 100h            | Indirect addr. <sup>(*)</sup> | 180h            |

| TMR0                          | 01h             | OPTION REG                    | 81h             | TMRO                                  | 101h            | OPTION REG                    | 181h            |

| PCL                           | 02h             | PCL                           | 82h             | PCL                                   | 102h            | PCL                           | 182h            |

| STATUS                        | 03h             | STATUS                        | 83h             | STATUS                                | 103h            | STATUS                        | 183h            |

| FSR                           | 04h             | FSR                           | 84h             | FSR                                   | 104h            | FSR                           | 184h            |

| PORTA                         | 05h             | TRISA                         | 85h             |                                       | 105h            |                               | 185h            |

| PORTB                         | 06h             | TRISB                         | 86h             | PORTB                                 | 106h            | TRISB                         | 186h            |

| PORTC                         | 07h             | TRISC                         | 87h             | · · · · · · · · · · · · · · · · · · · | 107h            |                               | 187h            |

| PORTD <sup>(1)</sup>          | 08h             | TRISD <sup>(1)</sup>          | 88h             |                                       | 108h            |                               | 188h            |

| PORTE <sup>(1)</sup>          | 09h             | TRISE <sup>(1)</sup>          | 89h             |                                       | 109h            |                               | 189h            |

| PCLATH                        | 0Ah             | PCLATH                        | 8Ah             | PCLATH                                | 10Ah            | PCLATH                        | 18Ah            |

| INTCON                        | 0Bh             | INTCON                        | 8Bh             | INTCON                                | 10Bh            | INTCON                        | 188h            |

| PIR1                          | 0Ch             | PIE1                          | 8Ch             | EEDATA                                | 10Ch            | EECON1                        | 18Ch            |

| PIR2                          | 0Dh             | PIE2                          | 8Dh             | EEADR                                 | 10Dh            | EECON2                        | 18Dh            |

| TMR1L                         | 0Eh             | PCON                          | 8Eh             | EEDATH                                | 10Eh            |                               | 18Eh            |

| TMR1H                         | OFh             | ···                           | 8Fh             | EEADRH                                | 10Fh            |                               | 18Fh            |

| TICON                         | 10h             |                               | 90h             |                                       | 110h            |                               | 190h            |

| TMR2                          | 11h             | SSPCON2                       | 91h             |                                       | 111h            | ·                             | 191h            |

| T2CON                         | 12h             | PR2                           | 92h             |                                       | 112h            |                               | 192h            |

| SSPBUF                        | 13h             | SSPADD                        | 93h             |                                       | 113h            |                               | 193h            |

| SSPCON                        | 14h             | SSPSTAT                       | 94h             |                                       | 114h            | 1                             | 194h            |

| CCPR1L                        | 15h             |                               | 95h             |                                       | 115h            |                               | 195h            |

| CCPR1H                        | 16h             |                               | 96h             |                                       | 116h            |                               | 196h            |

| CCP1CON                       | 17h             |                               | 97h             | General                               | 117h            | Generat<br>Purpose            | 197h            |

| RCSTA                         | 18h             | TXSTA                         | 98h             | Purpose<br>Register                   | 118h            | Register                      | 198h            |

| TXREG                         | 19h             | SPBRG                         | 99h             | 16 Bytes                              | 119h            | 16 Bytes                      | 199h            |

| RCREG                         | 1Ah             |                               | 9Ah             |                                       | 11Ah            |                               | 19Ah            |

| CCPR2L                        | 1Bh             |                               | 9Bh             |                                       | 11Bh            |                               | 19Bh            |

| CCPR2H                        | 1Ch             |                               | 9Ch             |                                       | 11Ch            |                               | 19Ch            |

| CCP2CON                       | 1Dh             |                               | 9Dh             |                                       | 11Dh            |                               | 19Dh            |

| ADRESH                        | 1Eh             | ADRESL                        | 9Eh             |                                       | 11Eh            |                               | 19Eh            |

| ADCON0                        | 1Fh             | ADCON1                        | 9Fh             |                                       | 11Fh            |                               | 19Fh            |

|                               | 20h             |                               | A0h             |                                       | 120h            |                               | 1AOh            |

| General<br>Purpose            |                 | General                       |                 | General<br>Purpose                    |                 | General                       |                 |

| Register                      |                 | Purpose<br>Register           |                 | Register                              |                 | Purpose<br>Register           |                 |

| 96 Bytes                      |                 | 80 Bytes                      | EFh             | 80 Bytes                              | 16Fh            | 80 Bytes                      | 1EFh            |

|                               |                 | accesses<br>70h-7Fh           | FOh             | accesses<br>70h-7Fh                   | 170h            | accesses<br>70h - 7Fh         | 1F0h            |

|                               | 7Eh             | (MCCO)                        | FFh             | FOR THE R                             | 17Fh            |                               | 1FFh            |

Unimplemented data memory locations, read as '0'.

\* Not a physical register.

Note 1: These registers are not implemented on the PIC16F876. 2: These registers are reserved, maintain these registers clear.

Data Page 7 of 10

### ADCON0 REGISTER (ADDRESS: 1Fh)

| <b>R/W</b> -0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0   | U-0 | R/W-0 |

|---------------|-------|-------|-------|-------|---------|-----|-------|

| ADCS1         | ADCS0 | CHS2  | CHS1  | CHS0  | GO/DONE |     | ADON  |

| bit 7         |       |       |       |       |         |     | bit 0 |

### ADCS1:ADCS0: A/D Conversion Clock Select bits

00 = Fosc/2

01 = Fosc/8

10 = Fosc/32

11 = FRC (clock derived from the internal A/D module RC oscillator)

### CHS2:CHS0: Analog Channel Select bits

000 = channel 0, (RA0/AN0)

001 = channel 1, (RA1/AN1)

010 = channel 2, (RA2/AN2)

011 = channel 3, (RA3/AN3)

100 = channel 4, (RA5/AN4)

101 = channel 5, (RE0/AN5)<sup>(1)</sup>

110 = channel 6, (RE1/AN6)<sup>(1)</sup> 111 = channel 7, (RE2/AN7)<sup>(1)</sup>

### GO/DONE: A/D Conversion Status bit

If ADON = 1:

1 = A/D conversion in progress (setting this bit starts the A/D conversion)

0 = A/D conversion not in progress (this bit is automatically cleared by hardware when the A/D conversion is complete)

Unimplemented: Read as '0'

### ADON: A/D On bit

с. . . . . . \$<sup>2</sup>. .

1 = A/D converter module is operating

0 = A/D converter module is shut-off and consumes no operating current

## ADCON1 REGISTER (ADDRESS 9Fh)

| U-0   | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| ADFM  |     |       |     | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 | -   |       |     |       |       | •     | bit 0 |

### ADFM: A/D Result Format Select bit

1 = Right justified. 6 Most Significant bits of ADRESH are read as '0'.

0 = Left justified. 6 Least Significant bits of ADRESL are read as '0'.

Unimplemented: Read as '0'

•

PCFG3:PCFG0: A/D Port Configuration Control bits:

| PCFG3:<br>PCFG0 | AN7 <sup>(1)</sup><br>RE2 | ANG <sup>(†)</sup><br>RE1 | AN5 <sup>(1)</sup><br>RE0 | AN4<br>RA5 | AN3<br>RA3 | AN2<br>RA2 | AN1<br>RA1 | AN0<br>RA0 | VREF+ | VREF- | CHAN/<br>Refs <sup>(2)</sup> |

|-----------------|---------------------------|---------------------------|---------------------------|------------|------------|------------|------------|------------|-------|-------|------------------------------|

| 0000            | A                         | A                         | Α                         | Α          | A          | A          | Α          | A          | VDD   | Vss   | 8/0                          |

| 0001            | A                         | A                         | Α                         | A          | VREF+      | Α          | A          | A          | RA3   | Vss   | 7/1                          |

| 0010            | D                         | D                         | D                         | Α          | A          | Α          | A          | A          | VDD   | Vss   | 5/0                          |

| 0011            | D                         | D                         | D                         | A          | VREF+      | A          | A          | A          | RA3   | Vss   | 4/1                          |

| 0100            | D                         | D                         | D                         | D          | A          | D          | A          | A          | VDD   | Vss   | 3/0                          |

| 0101            | D                         | D                         | Ð                         | D          | VREF+      | D          | Α          | A          | RA3   | Vss   | 2/1                          |

| 011x            | D                         | D                         | D                         | D          | D          | D          | D          | D          | VDD   | Vss   | 0/0                          |

| 1000            | A                         | A                         | Α                         | A          | VREF+      | VREF-      | A          | A          | RA3   | RA2   | 6/2                          |

| 1001            | D                         | D                         | Α                         | A          | A          | A          | . <b>A</b> | A          | VDD   | Vss   | 6/0                          |

| 1010            | Ð                         | D                         | Α                         | Α          | VREF+      | A          | A          | A          | RA3   | Vss   | 5/1                          |

| 1011            | D                         | D                         | Α                         | A          | VREF+      | VREF-      | A          | A          | RA3   | RA2   | 4/2                          |

| 1100            | D                         | D                         | D                         | A          | VREF+      | VREF-      | A          | A          | RA3   | RA2   | 3/2                          |

| 1101            | D                         | D                         | D                         | D          | VREF+      | VREF-      | A          | A          | RA3   | RA2   | 2/2                          |

| 1110            | D                         | D                         | D                         | D          | D          | D          | D          | A          | VDO   | Vss   | 1/0                          |

| 1111            | D                         | D                         | D                         | D          | VREF+      | VREF-      | D          | A          | RA3   | RA2   | 1/2                          |

A = Analog input D = Digital I/O

Note 1: These channels are not available on PIC16F873/876 devices.

2: This column indicates the number of analog channels available as A/D inputs and the number of analog channels used as voltage reference inputs.

| Legend:            |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

Data Page 9 of 10

### Data Page 10 of 10