#### UNIVERSITY OF SWAZILAND

FACULTY OF SCIENCE AND ENGINEERING DEPARTMENT OF PHYSICS

MAIN EXAMINATION2012/13TITLE OF PAPER:DIGITAL ELECTRONICSCOURSE NUMBER:P411TIME ALLOWED:3 HOURS

**INSTRUCTIONS:**

ANSWER ANY FOUR OUT OF FIVE QUESTIONS.

EACH QUESTION CARRIES 25 MARKS.

MARKS FOR DIFFERENT SECTIONS ARE SHOWN ENCLOSED IN SQUARE BRACKETS.

THIS PAPER HAS 7 PAGES INCLUDING THIS PAGE.

DO NOT OPEN THE PAPER UNTIL PERMISSION HAS BEEN GIVEN BY THE INVIGILATOR.

| 1 (a) (i) The 7's complement of a certain octal number is 5264. Determine the hexadecimal equivalent of that octal number.                                                                                                                                                     | [3]                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| <ul> <li>(ii) Convert the hexadecimal number 2B6D.5AB<sub>16</sub> to its equivatent decimal<br/>number.</li> </ul>                                                                                                                                                            | [3]                 |

| (b) (i) Subract 2B6D.5 <sub>16</sub> from 5A6BD.2 <sub>16</sub> .                                                                                                                                                                                                              | [3]                 |

| <ul> <li>(ii) Find the equivalent decimal value of the following BCD coded number:<br/>10011101100011<sub>BCD</sub>.</li> </ul>                                                                                                                                                | [2]                 |

| (c) (i) Convert the straight binary number 110011 <sub>2</sub> to its Gray code equivalent.                                                                                                                                                                                    | [2]                 |

| (ii) Convert the 2's complement of the quinary number 4145 into hexadecimation                                                                                                                                                                                                 | al. <b>[6]</b>      |

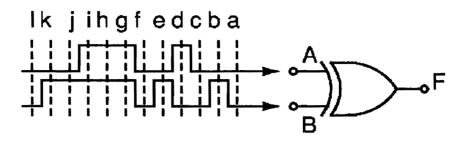

| (d) Consider the two signals simultaneously entering the EX-OR gate in figure<br>Appendix A. Make a table listing the binary outputs corresponding to the in<br>points labeled a, b,l.                                                                                         |                     |

| 2 (a) Show how you would implement a four-input EX-OR function using two-inp<br>EX-OR gates.                                                                                                                                                                                   | out<br>[ <b>4</b> ] |

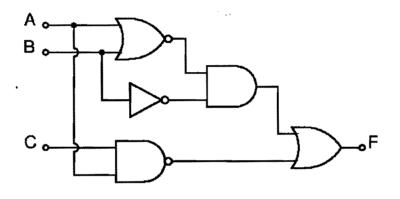

| (b) Write the Boolean expression for the logic diagram in figure 2 of<br>Appendix A.                                                                                                                                                                                           | [5]                 |

| (c) Convert the following Boolean expressions to their <b>simplest non</b> -standard S forms:                                                                                                                                                                                  | OP                  |

| (i) $F = (\overline{A + \overline{B}C + A\overline{B}});$                                                                                                                                                                                                                      | [4]                 |

| (ii) $F = \overline{(AB + AC)}$ .                                                                                                                                                                                                                                              | [4]                 |

| (d) Minimize the Boolean expression for the logic function<br>$F(ABCD) = AB\overline{C}D + A\overline{B}\overline{C}\overline{D} + \overline{B}CD + \overline{A}\overline{B} + \overline{A}B\overline{C}D + AB\overline{C}D + A\overline{B}\overline{C}$ using a Karnaugh map. | [8]                 |

- **3** (a) Use the transposition theorem to prove that  $L(M + \overline{N}) + \overline{L}\overline{P}Q = (L + \overline{P}Q)(\overline{L} + M + \overline{N}).$ [3]

- (b) (i) Make the truth table for the <u>sum function</u>, S of a full adder with three inputs A, B and C. Do not include the carry-out function. [2]

- (ii) Make a truth table for an even parity generator circuit which has three inputs A, B and C with one output P which is the parity bit. [2]

- (iii) Show how you would implement the functions S and P using a single logic gate.

- (c) The data sheet of a certain eight-bit A/D converter lists the following specifications: the resolution is eight bits, the full-scale error is 0.02 % of full scale and the full-scale analogue input is +5 V. Determine:

| (i) the quantized error | (in volts); | [3] |

|-------------------------|-------------|-----|

|-------------------------|-------------|-----|

(ii) the total possible error (in volts). [3]

- (d) A certain eight-bit D/A converter has a full-scale output of 5 mV and a full-scale error of ±0.25%. Determine the range of expected analogue outputs for a digital input of 10000010.

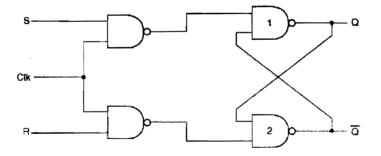

- 4 (a) Figure 3, in Appendix A, shows a labeled logic circuit of a four-NAND gate RS flip flop. Copy and complete Table 1 of Appendix B with the various signals at the inputs and output of the clocked RS flip flop. [4]

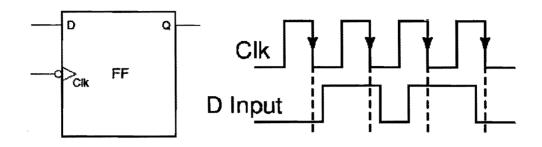

- (b) **Figure 4**, of **Appendix A**, shows a negative edge triggered D-type flip flop. The clock pulse and the D-input are shown in a timing waveform diagram to the right of the flip flop. Copy the timing waveform diagram and draw the waveform of the output, Q just below the D-input waveform. Use the same clock pulse timing.[6]

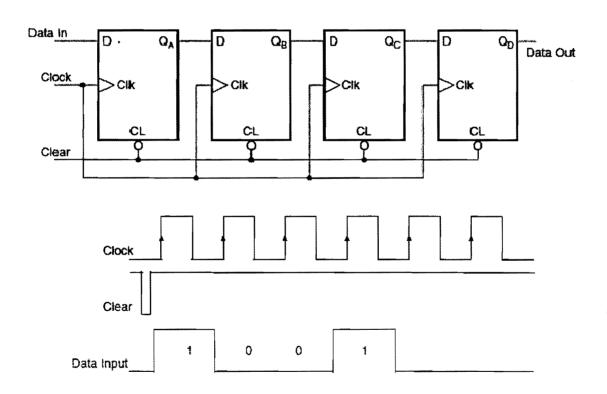

- (c) Figure 5, in Appendix A, shows a 4-bit shift register. The clock pulse, clear signal and data input are shown in a timing waveform diagram below the register. Copy the timing waveform diagram and draw the waveforms of the outputs, Q<sub>A</sub>, Q<sub>B</sub>, Q<sub>C</sub> and Q<sub>D</sub> just below the data input waveform, using the same clock pulse timing. [8]

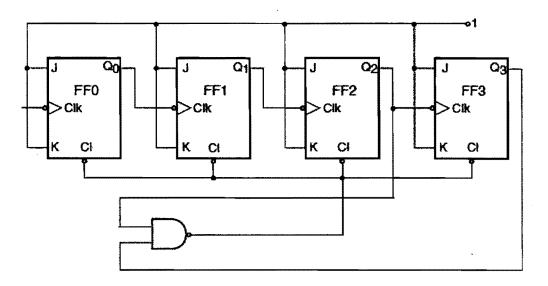

- (d) Identify the logic circuit in **figure 6** of **Appendix A** and explain how it functions. [7]

- 5 (a) RAM chips are available in the memory capacities ranging from 2 kB to 32 MB, here, the terms 'kilo' (k) and 'mega' (M) are approximations that do not exactly represent 10<sup>3</sup> and 10<sup>6</sup> bytes of actual memory respectively. How many bytes of actual memory do these terms represent? [2]

- (b) A certain ROM is capable of sorting 16 kB of data. If the internal architecture of the ROM uses a square matrix of registers, determine:

| (i) the number of registers in each row and column; | [5] |

|-----------------------------------------------------|-----|

|                                                     |     |

(ii) the total number of address inputs.

[5]

- (c) It is desired to design a microcontroller-based periodic signal generator with minimum and maximum time period specifications of 125 ns and 100 ms. What should the system clock frequency be?

- (d) A certain microcontroller has an on-chip 16-bit counter/timer system. It is used to measure the width of an input pulse. The microcontroller has been programmed to measure the time of occurrence of rising and falling edges of an input pulse on a certain I/O pin. If the microcontroller uses an 8 MHz clock and the count values observed at the time of occurrence of rising and falling edges of the input pulse are 001F and 00F1 (in hex), determine the pulse width as measured by the microcontroller.

### **APPENDIX A – DIAGRAMS**

Figure 2

Figure 3

,

Figure 5

,

Figure 6

## **APPENDIX B – TABLE**

#### Table 1

| Inp | outs | Output before<br>the clock pulse | Output after<br>the clock pulse |

|-----|------|----------------------------------|---------------------------------|

| S   | R    | Q                                | Q                               |

| 0   | 0    | 0                                |                                 |

| 0   | 0    | 1                                |                                 |

| 0   | 1    | 0                                |                                 |

| 0   | 1 .  | 1                                |                                 |

| 1   | 0    | 0                                |                                 |

| 1   | 0    | 1                                |                                 |

| 1   | 1    | 0                                |                                 |

| 1   | 11   | 1                                |                                 |

# END OF P411 EXAMINATION